|

||

|

*停權中*

加入日期: Jan 2008

文章: 1,281

|

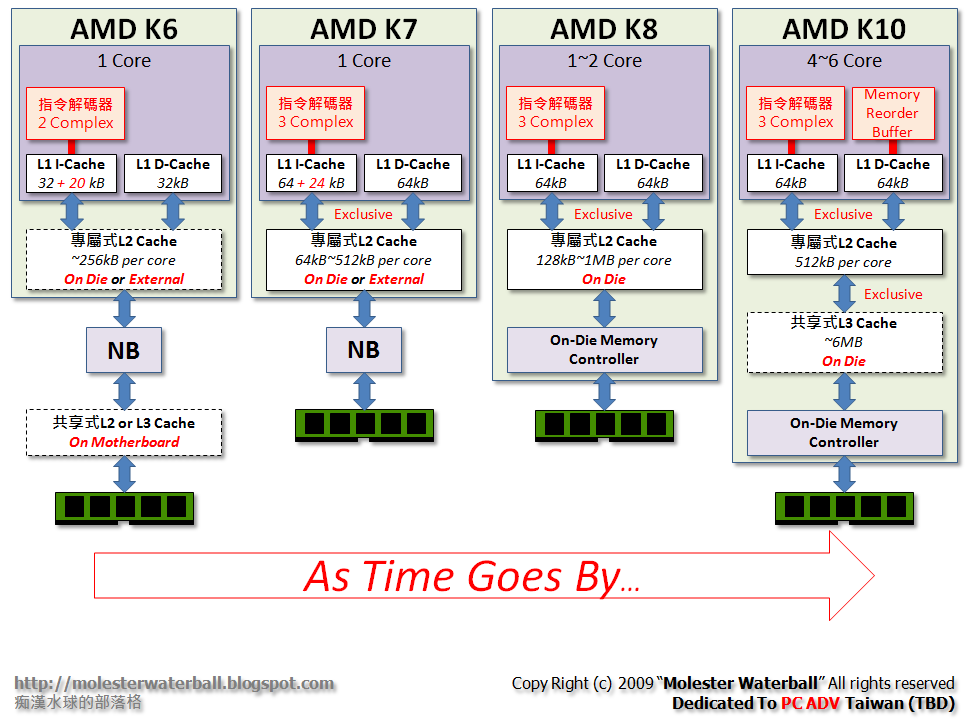

CPU cache hierarchy

來源(http://molesterwaterball.blogspot.com/)

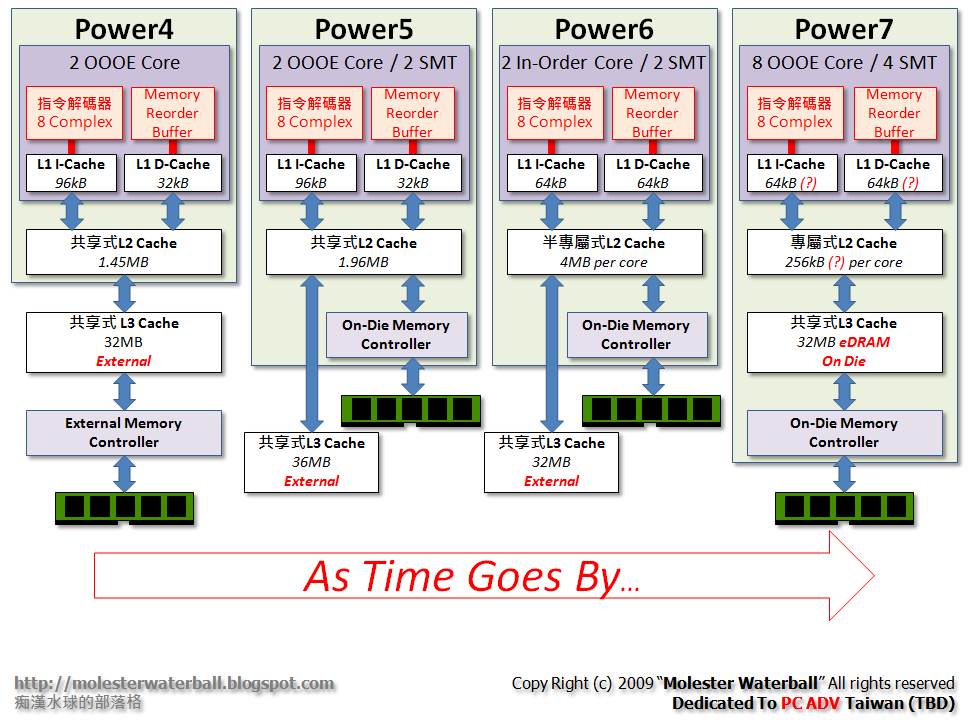

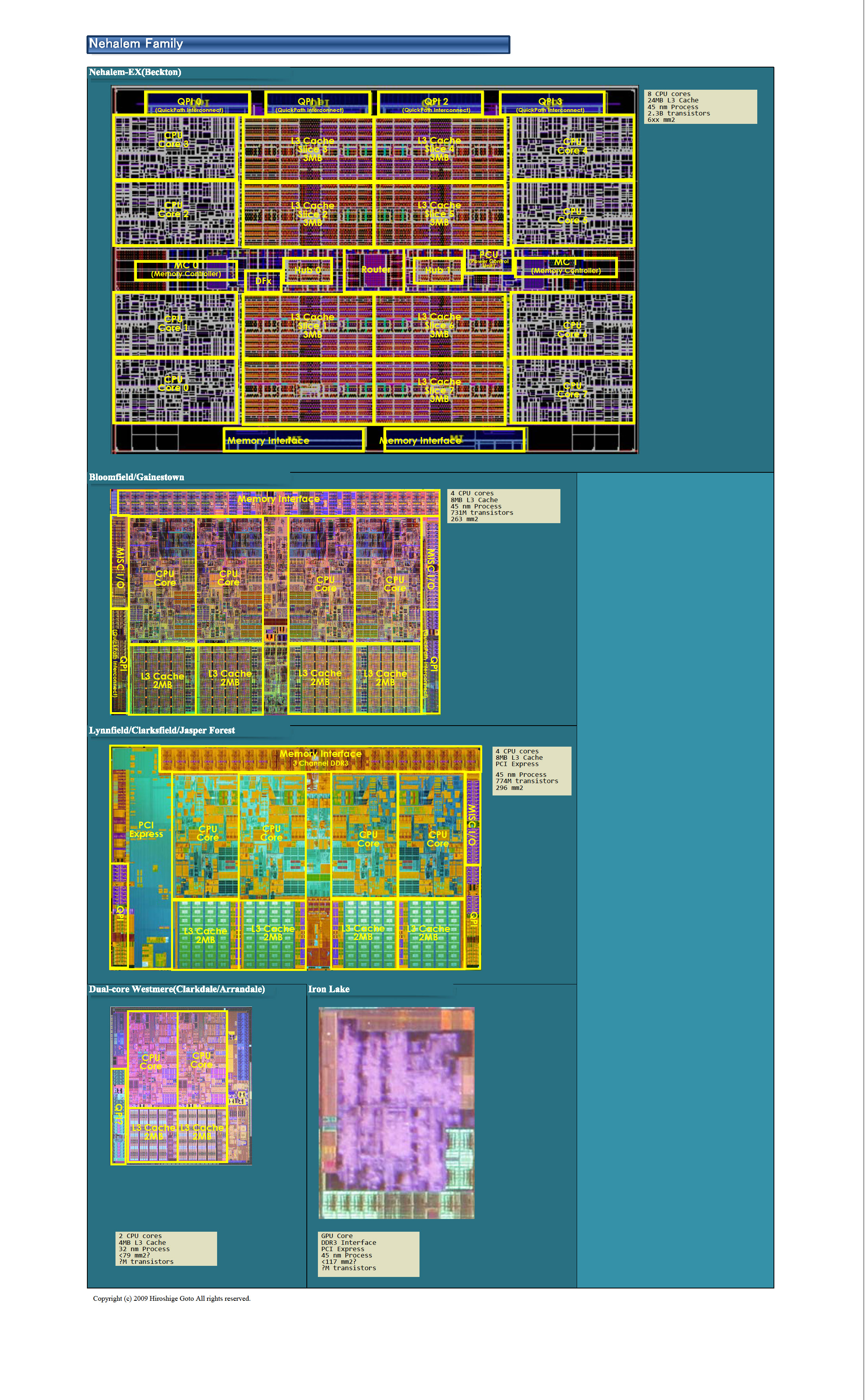

Intel x86 CPU cache hierarchy  AMD x86 CPU cache hierarchy  IBM POWER 4/5/6/7 cache hierarchy  |

|||||||

|

|

|

Golden Member

加入日期: Aug 2004

文章: 2,892

|

Power5 開始有SMT 1顆實體雙核可分別開2個Thread (130nm)

DDR/DDRII memory Power6 一樣 時脈拉到5GHz (65nm) DDR II memory Power7 目前看起來原生8核 每核心可以跑4個Thread 一顆實體跑32個thread (45nm) DDR III memory 另外..單一個時脈周期兩次浮點運算...多組記憶體控制器

__________________

|

||

|

|

|

*停權中*

加入日期: Jan 2008

文章: 1,281

|

引用:

我第一次接觸 Power 7 的規格,看起來超強的樣子,不過我更好奇它的 32M L3 要用掉多少 Die 面積  |

|

|

|

|

Senior Member

加入日期: Oct 2001 您的住址: 彰化縣xx鄉

文章: 1,199

|

我更好奇

這種東西要賣多少錢 以商業機器公司......

__________________

1.真象可能不只有一個 2.時間能證明一切 最近才知道..."社會文盲"有很多,一邊哀鳴著別個油多便宜 但他們跟本不知道是奴役著3億人外的其他人類所得的血汗油價! http://tw.stock.yahoo.com/news_content/url/d/a/110510/2/2kwvo.html 上阿! 刪掉補助款! 為了世界的未來+和平!! 請大家多多抗韓!!!!!! |

|

|

|

Golden Member

加入日期: Aug 2004

文章: 2,892

|

引用:

就目前放出來的消息 Die 看起來是這樣 http://www.edn.com/article/CA6686259.html

__________________

|

|

|

|

|

*停權中*

加入日期: Jan 2008

文章: 1,281

|

瞭解,看起來非常壯觀

|

|

|

|

*停權中*

加入日期: Jan 2008

文章: 1,281

|

還有 Nehalem-EX 的 24M L3 也非常壯觀

|

|

|