|

||

|

Golden Member

加入日期: Dec 2001

文章: 2,930

|

剛看到的Skylake-S Core i5/i7規格

http://www.cpu-world.com/news_2015/...CPU_lineup.html 4核TDP 65W  那2核不知道能壓到多少  |

|||||||

|

|

|

*停權中*

加入日期: Apr 2015 您的住址: 溫室

文章: 147

|

引用:

如果Zen真的有打算出16核 我猜是像Atom那種小核心 不會是主戰場 Zen給主流PC用的還是4~8核 效能最多高出i5一些 某幾項測試能贏i7一點 AMD不是intel 沒本事玩兩個腳位 FX AM3+弄的上不上、下不下的  下一代連ARM都能用同一個腳位 火力集中下 再怎麼樣也比現在好吧 |

|||

|

|

|

*停權中*

加入日期: Apr 2015

文章: 58

|

引用:

i386當年之所以只有8gprs最大原因是因為386當年只是應急下的向下相容的過渡產物. 既然是過度產物當然不會受到那群銀行業打滾的肥貓股東所重視 要不是iapx32難產intel本來可是要放生8086呢. 就像itanium對netburst,yamhill一樣. 對於intel那群肥貓股東們而言i386只是個過渡產品他們更注重iapx32, iapx32是stack machine based而且完全沒有register...而之所以這麼搞就是因為產品延伸性與獲利高成本更低與犧牲相對應的效能為代價來達成公司營收. 相較之下雖然x86效能更高但是獲利延伸性輸給stack machine 而因為transistor少且沒有integer register時脈可以拉非常高而且高階市場可以用串聯來達成效能最佳化而不用每次花大錢做 new uArh. 要不是因為當年intel工程師與股東之間長時間的內鬥x86也不會長年擺爛導致於後來想重視的時候已經很難再做改變 |

|

|

|

|

Major Member

加入日期: Jan 2002

文章: 159

|

iapx32如果是指iAPX432 ,當年最大阻礙還是同樣source code,iAPX432就是比80286慢

而且還用比較多 transistors, 6 ~ 321bit的可變長度指令要平行解碼就暈倒了... 從以前到現在,mem to mem都比reg to reg慢,不太懂stack會快的理由

__________________

|

|

|

|

*停權中*

加入日期: Apr 2015

文章: 58

|

引用:

事實上iapx研發時期極長 從1977年就開始研發直到1992年才放棄的(不過主因是被itanium取代, 而且過於燒錢卻效能比不過x86而終止)而iapx"4"32只是其中一個晚期代號而已 至於stack based的memory to memory對register based不具競爭力的見解是建立在modern processor architecture上 雖然經過optimized後對x86/risc而言同頻依然相對貧弱來說iapx卻是第一個使用cache subsystem跟instruction pipelining的uArh, 而transistor相較286/386來的多也是因為cache的原因 如果拿掉cache的話其core transistor count只有286的一半. 論同期只有inmos transputer跟wdc 65816有這個feature. 至於其他如8086,i386,68k,mips等同期產品由於沒有cache+pipeline雖然在home use上效能強壓stack machine但是在處理raw large data時卻因為integer register相對於cache subsystem而言太小了而顯得雞肋. 而且由於stack machine時脈好拉(300mhz default, 同期i386dx/68k只有16~33mhz )使得以前所有的弱點被暫時掩蓋了. 不過這些優勢在486以後就消失了...... 噢~忘了說iapx團隊就是後來惡名昭彰的netburst創造者. 至於stack machine的fix length opcoding其實最大問題是因為沒有instruction decoder而全靠logical unit暴力執行而產生大量waste cycle...只能說其設計過於短視了 此文章於 2015-05-05 02:24 PM 被 flatmode 編輯. |

|

|

|

|

Junior Member

加入日期: Feb 2005

文章: 713

|

引用:

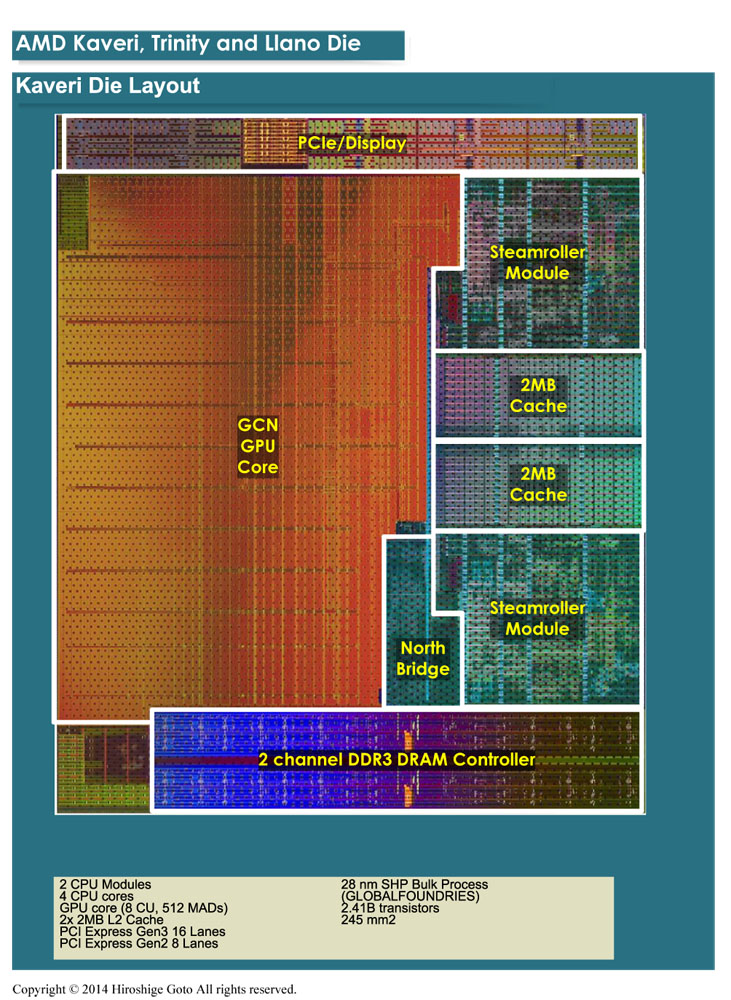

假設28nm SHP ,cpu非module 16 core,還要塞至少4~8組GCN core 認真的嗎 此文章於 2015-05-05 02:56 PM 被 wuciboy 編輯. |

|

|

|

|

*停權中*

加入日期: Apr 2015 您的住址: 溫室

文章: 147

|

引用:

我說的是下一代的Zen 用的是14nm FinFET 而且那個16核心的可能是類似Xeon Phi這種運算卡 GPU會有 不知道配幾核的GPU CPU跟GPU都會比DT版的還要再簡化 簡單來說16核的產品是AMD以Xeon Phi為假想敵的HSA運算卡 以上是我的猜想 --- A closer look at Intel’s 72-core x86 Knights Landing chip and the race to exascale computing http://www.itproportal.com/2013/11/...cale-computing/  |

|

|

|

|

Junior Member

加入日期: Feb 2005

文章: 713

|

引用:

我知道你在說Zen,就算吃了三星神油但最後會不會是14/16nm FinFET,等AMD自己想公布在來說吧 此文章於 2015-05-05 03:31 PM 被 wuciboy 編輯. |

|

|

|

|

*停權中*

加入日期: Apr 2015 您的住址: 溫室

文章: 147

|

引用:

三星沒有神油 intel才有 那個16核心也是尚未證實的消息 說不定根本就沒有16核心的產品 |

|

|

|

|

Junior Member

加入日期: Feb 2005

文章: 713

|

引用:

各站AMD APU/GPU的rumor表示 |

|

|

|