|

||

|

Master Member

加入日期: Sep 2003

文章: 2,102

|

AMD推土機架構再探:核心不再是簡單計數

http://news.mydrivers.com/1/150/150209.htm

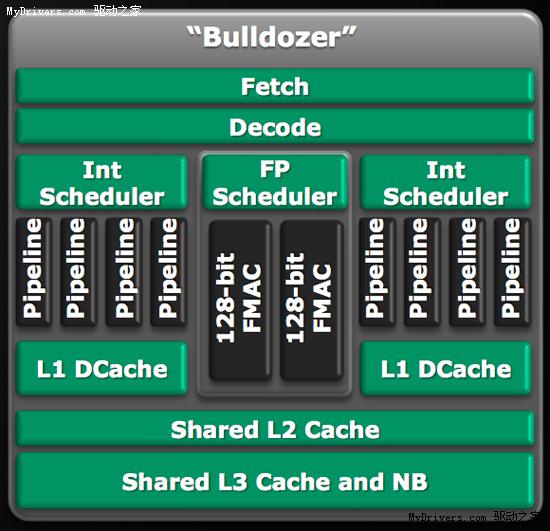

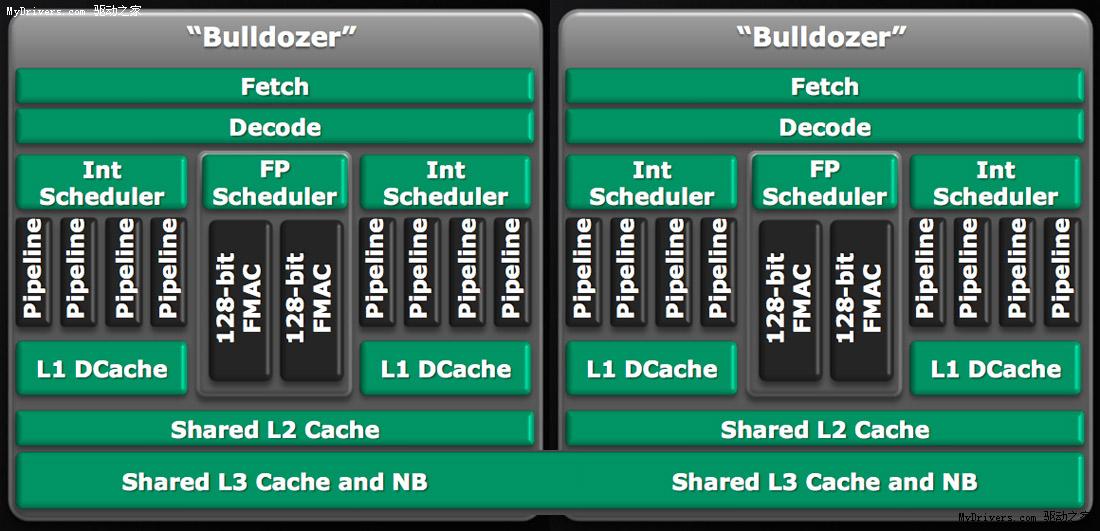

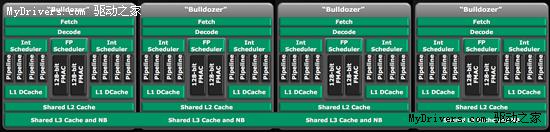

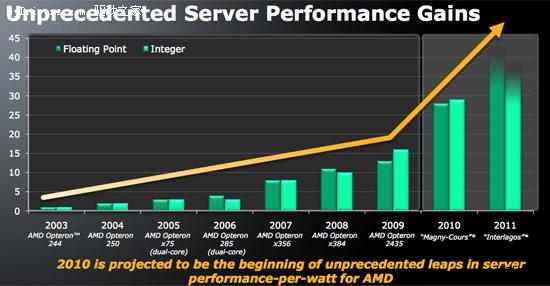

三週前,AMD首次公開了下一代微處理器架構「推土機」(Bulldozer)的架構細節,提出新觀念的同時也留下了個問題:以後的處理器核心數量該怎麼計算? Intel Nehalem架構支持單核心雙線程,而AMD推土機架構則頗有點兒反其道而行之的意思,將每兩個核心捆綁在一塊兒,稱之為一個「推土機模塊」(Bulldozer Module),讓其中著兩個核心既有各自獨立的執行管線、整數調度器和一級緩存,也有共享的預取和解碼單元、浮點調度器(和兩個128-bit FMAC乘法累加單元)、二級緩存。 Intel在Core/Nehalem微架構中使用一個統一調度器處理所有指令,不管是整數的還是浮點的,而AMD推土機架構將它們獨立開來。AMD表示,每個推土機模塊都有一個浮點調度器,輔以兩個128-bit FMAC,而分配給核心的每個線程都可以使用任意一個FMAC單元;如果一個線程是純整數的,另一個就可以將所有浮點執行資源據為己有。 另外AMD相信,常規服務器工作負載量中有80%都是純整數操作,所以才給每個推土機模塊配備了兩個整數調度器,每個核心一個。  那麼在AMD路線圖上的新架構四核心處理器指的是四個這樣的模塊呢,還是四個計算核心呢? AMD對此給出的回覆是:「將每個擁有雙整數核心的推土機模塊視為一個獨立的單元,就對了。」顯然,AMD在這裡刻意迴避了單純的核心數量問題,更強調兩兩組成的有機整體,所以在面對推土機架構處理器的時候我們可以說它是四核心、八核心的,也可以說是雙模塊、四模塊的。或許,以後不會再有奇數核心了,因為推土機的每個模塊都是整體的,看起來不能單獨屏蔽其中一個核心。  雙模塊四核心推土機處理器示意圖(所有核心共享三級緩存和北橋)  四模塊八核心示意圖 Intel的超線程技術讓處理器核心面積增加了不到5%,可帶來最多30%的性能提升,其中浮點7%、整數13%,當然實際應用中差異很大。 AMD推土機模塊使用兩個整數核心增加的核心面積則有50%左右,但AMD表示這在線程代碼上獲得的性能提升最多能有80%。當然,不要指望新架構就能帶來翻天覆地的變化。根據路線圖,「贊比西河」(Zambezi)會有四核心和八核心版本(雙模塊和四模塊),其中四核心的整數性能大約比頻率類似的Phenom II X4高出10-35%,八核心的將成為一個線程怪獸。  ------------------------------------------------------------------------ 先不管什麼時候出 還是真的假的 討論面積與效能 看起來好像不錯 Phenom II X4 面積為 400% 「贊比西河」(Zambezi)會有四核心 面積為 300% 且效能提高10-35%

__________________

[ExtremeTech]VGAMaster |

|||||||

|

|

|

*停權中*

加入日期: Apr 2009

文章: 52

|

個人蠻看好山貓的,2cores 跑 1thread,效能至少提升 50%,還不用像 HT 要看軟件有無支援

|

||

|

|

|

Junior Member

加入日期: Oct 2002

文章: 707

|

最棒的作法是,可以讓使用者自行決定是否讓多個cpu在同一thread運作,如果可以在OS中做調整是最好的

因為支援多核心或是HT的程式,基本上還是用多核心或是HT下去跑才會快 但如果程式只支援單核心,那推土機的架構將會非常的吃香! |

|

|

|

Elite Member

加入日期: Dec 2006 您的住址: Taipei

文章: 8,344

|

多核加持單線程.....如果是這樣, 說不定高階顯卡需要的高效能CPU可以改用AMD試試.

|

|

|

|

Senior Member

加入日期: Nov 2004

文章: 1,216

|

1.這是不是ATI HD5xxx系列的靈感?

2.新構想和現實配合否,還是要時間去考驗... 3.amd的製程是否跟得上?不要說是四核cpu,做成晶片面積變成比8核還大,到時玩家沒電爐,用這cpu來煮開水剛好... 此文章於 2009-12-02 10:13 AM 被 ylc2 編輯. |

|

|

|

*停權中*

加入日期: Jan 2008

文章: 1,281

|

Bulldozer Module 簡單講就是在原始核心設計的基礎上再塞入一個整數執行單元罷了

一來晶粒面積(成本)增加有限、二來給人核心數倍增的錯覺,以 AMD 現在的處境來說這招使得還算可以 |

|

|

|

Junior Member

加入日期: Jan 2003

文章: 967

|

引用:

抱歉小弟的沒有CPU核心架構的概念,底下白痴問題可以的話請幫小弟解惑^^; 看圖是一個FPU沒錯....... 不過看FPU裡面有兩個128 Bit的FMAC.......... 這樣算是有兩個浮點數運算單位嗎??還是只能算一個?? 另外既然都做兩個128Bit的FMAC了,有可能可以延伸成一個256Bit的FMAC嘛? 不知道AMD有沒有暗蓋東西沒發佈 XD |

|

|

|

|

*停權中*

加入日期: Jan 2008

文章: 1,281

|

引用:

示意圖只是概略描述,並未將完整的架構畫出來 例如 FADD、FMUL、FSTORE 等都並未標示 我認為這些東西合起來才能算是一個完整的單元 此文章於 2009-12-02 03:03 PM 被 visionary_pcdvd 編輯. |

|

|

|

|

Junior Member

加入日期: Sep 2001 您的住址: 1342萬光年外

文章: 896

|

引用:

同時脈的Nehalem(I5、I7)效能大概是Phenom II的150%, 如果真的 Bulldozer同時脈效能能夠較Phenom II提升 50%, 那麼至少可以平起平坐,不再是被Nehalem架構打假的.. 假設這種架構下的效能真的OK, 那麼就只剩Bulldozer時脈的問題了, 要是空冷只能2-3Ghz,那也應該是蠻慘的..

__________________

|

|

|

|

|

Power Member

加入日期: Oct 2004

文章: 594

|

AMD原廠工程師John Fruehe說die size才只增加5% 跟之前的50%有很大的出入...

If you were to strip one integer core out of each of the bulldozer module, moving them from two integer cores to one, you would only reduce the size of the unit by ~5% as well. So, for 5%, you can have SMT (10-20% increase in performance, or negative increase in performance) or you can have bulldozer (80% increase in performance.) The choice is yours in 2011, buy whichever you believe is the better architecture. I just can't see someone wanting 10-20% when you can get so much more with Bulldozer. 來源: http://www.amdzone.com/phpbb3/viewt...d768e5&start=50 |

|

|