引用:

|

作者liccaba

等一下 我再重新解釋這2句話的定義

在低電壓下有 37 %效能增進 表示的應該是在低電壓下才有效能增進

如果把電壓調高就沒有效能增進 意思也就是在低電壓下可以跑出比之前更高的效能

在固定效能下有降低 >50% 功耗 表示的應該是在某個預設時脈下 功耗可以降低

但時脈調高後 功耗就會暴增 意思也就是在低時脈下可以比之前更省電

如果是這樣 受益最大的應該是筆電和HTPC和低階CPU 每瓦效能可以大幅提高

但中高階的應該就受益不到 這就好像是一種邊際效應一樣

當你要突破這條界線時 所要付出代價必需增加好幾倍

我玩線上遊戲也是這樣 頂的裝備比普通的裝備好1~2倍 但價格卻會暴增10~20倍以上

|

我不是相關專業出身 所以有誤還請糾正

這邊的電晶體效能與耗電都是跟 32nm Bulk 製程比較 (這次P1270 製程還有導入 High-K 跟 Tri-gate)

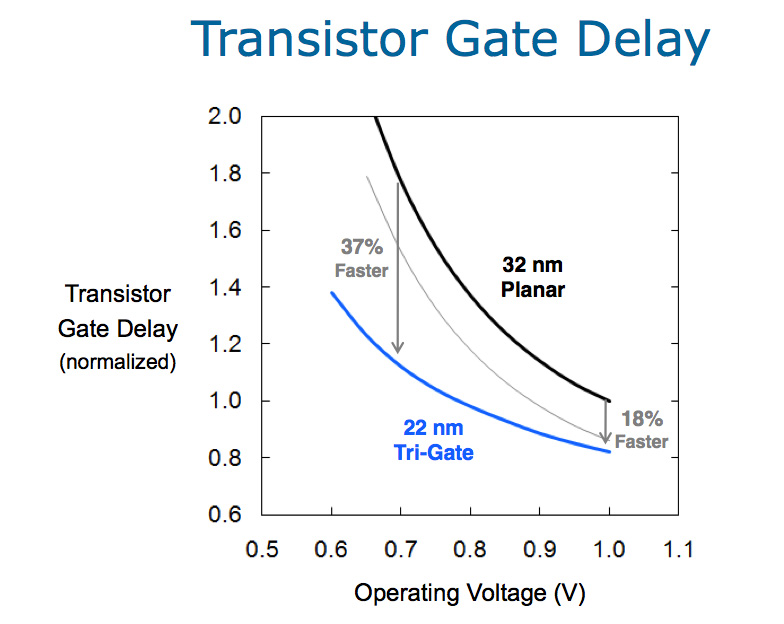

討論電晶體特性都會討論 Delay (Performance, 頻率) / Leakage (Power Consumption) 與電壓之間的關係

通常而言 電壓越大 Delay 越低, Leakage 越大, 製程間的特性曲線也不太一樣

引自pc.watch

在相較於32nm Bulk 製程, 22nm Tri-gate 可以在相同頻率下以75% - 80%的作業電壓下作業, Active Power 有50%的降低.

引自anandtech

在固定電壓狀況下, 在低電壓(0.7)有37%的效能增進, 在高電壓(1V) 也有18%增進..

這些特性幾乎有跨兩個Process node的表現...