(三)、MAX Memory

首先,我們必須知道,記憶體參數優化對於超頻系統影響甚鉅,但其提供的助益卻相對較小。切記!!唯有已經確定了您的Max CPU、Max HTT與Max Memory時脈後,方進行參數優化。

您可以先跳過參數部份,直接參考項次5. 並以SPD值進行DRAM超頻。

1.認識您的DRAM參數

CAS# latency (Tcl)

注意:此項為DRAM最重要之參數優化項.

2、2.5和3 ns

全名: 行位址控制器延遲時間(CAS Latency):通常簡稱CL。

CAS latency是指對DRAM晶片上某一行下達要求所需要的時間,Latency是計算延遲的單位,所以“CL2” CAS latency系數指延遲兩個時鐘週期,

而“CL3” latency系數指延遲三個時鐘週期。SDRAM剛推出時,製造CAS latency系數低於CL2的晶片很困難。

雖然有些指示要求CL2,但許多模組在CAS latency系數為CL3時仍可正常運作。CAS latency中解釋是CAS"Column Adress Strobe"將行位址送出後需過幾個T後第一筆資料才能ready for read,是一種read latency,這東西對效能影響很大.(wbj 2006)

RAS# to CAS# Delay (Trcd)

注意:此項為DRAM次要之參數優化項

2T(週期)~7T

全名: 列位址至行位址延遲時間(Row Adress Strobe,列位址控制器)to CAS(Column Adress Strobe,行位址控制器)。

記憶體控制器會先送出列(ROW)的位址(例如第2列),然後RAM收到列的位置後,經過一段時間,才會再傳送行(Column)的位址,而這一段時間就是RAS Delay。

Row precharge Time (Trp)

2T(週期)~7T

全名: 列位址控制器預充電時間(RAS Precharge、Precharge to active) 。

對迴路作預充電所需的時脈循環數,以決定列位址。

Min RAS# active time(Tras)

5T(週期)~12T

全名:列活躍時間(Row Active Timing)。

這是指在同一個bank下,存取不同row時必須將先前開啟(active)的row關閉(precharge)後才能開啟其他的row,而這個數字就是開啟一個row到能把它關閉的最短的時間. (wbj 2006)

Row Cycle Time(tRC)

全名:列迴圈時間 (Random read or write cycle time 。Cpu - Z顯示為Bank Cycle Time (Trc) )

此項Bios調整設定,控制了記憶體模組的 Row Cycle Time。Trc 數值決定記憶體一個完整的循環週期時間,(從 row activation up to the precharging of the active row 為止)

公式 tRC= tRAS + tRP

所以當tRAS與tRP最小,您可以獲得最小的Trc值。

因此,要獲得Trc值,您需要先確定您的最小 tRAS與 tRP。

如果您設定的Trc值,比tRAS+tRP還小...記憶體在傳輸訊息時,可能發生一個新的循環在記憶體重新充滿電之前開始,這將造成資訊喪失或是中斷。又如果您設定的Trc值過大。則新的週期開始之前,將會有不需要的等待時間(延遲)。

Idle Cycle Limit (DRAM Idle Timer)

值0~256。

此值決定了"記憶體在強制關閉預先充電的分頁空間之前,記憶體所有的循環週期數目"

換句話說,該值決定"在調停器中斷/強制重新預先充電該分頁之前,該記憶體分頁可以被讀取的次數" 此值對於記憶體頻寬影響甚小,對穩定性影響甚大。

所以如果您的記憶體體質較差,建議您不要設定過大的值,因為這將造成不穩定。

如果您的DRAM系出名門,可以建議設定在16~32 數值之間。

在華邦曾經推出的BH-5顆粒,甚至可以設定為16。

固此值越小,傳輸效能越快。

2.什麼是 1、2T CMD(1T/2T Command Rate)

(Command Rate、MA 1T/2T Select)當記憶體要求傳送、讀取資料區間"定址記憶體模組和記憶體晶片的時脈循環"所需時間。

-1T擁有較少的延遲,較佳的系統記憶體效能。卻較差的相容性。適合您的DIMM未插滿時。

-2T擁有較久的延遲、差很多的系統記憶體較能。較高的相容性、穩定性。適合您的DIMM已全部插滿時。

這邊我們建議設定為1T。

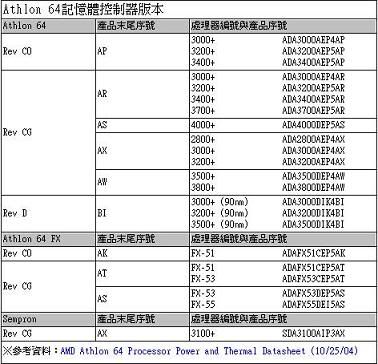

K8/C0 僅支援1T、D0支援2T。在CPU-Z可知。

3.什麼是SPD(Serial Presence Detect) 記憶體參數串列偵測

3.什麼是SPD(Serial Presence Detect) 記憶體參數串列偵測

-一般記憶體模組上,會多一顆小晶片,這就是具備SPD能力的記憶體,SPD是一個8針的256位元組的"可讀寫可編程唯讀記憶體晶片"。

-一般位在記憶體條正面的右側,記錄著記憶體的速度、容量、電壓與行、列位址帶寬等參數資訊。

-當開機時BIOS將自動讀取SPD中的資訊,節省開機Bios偵測的時間。

-若是需要手動調整記憶體參數則必須將Bios 中By SPD 設為手動。

4.DRAM參數設定 順序為(Tcl) - (Trcd) - (Trp) - (Tras)

-您希望追求記憶體最大頻寬者。

我建議CL2.5-4-3-7 1T /2.6~2.9v。

理想值=CL2.5-3-3-6 1T/2.6~2.8v

-您希望追求記憶體最快傳輸效能者。

我建議CL2-2-2-7 1T /2.6~2.9v。

理想值=CL2-2-2-5 1T/2.6~2.7v

-參考以下設定可獲得最佳頻寬並進一步提升記憶體效能。

(此部份僅供進階玩家設定,且並非所有主機板Bios皆支援調整)

1.儲存循環時間(Row cycleime) 請設為7T

2.Row refresh cycle time 請設為AUTO

3.Row to Row delay 請設為2T

4.Write recovery time 請設為2T

5.Write to Read delay 請設為1T

6.Read to Write delay 請設為2T

7.Refresh period 請設為3120 Cycles(1X 3120 Cycles)

-DDR500以上,建議設CL=3。

一般而言DDR400(200Mhz)記憶體最佳優化為 CL2-2-2-5,DDR600(300Mhz)記憶體最佳優化為

CL2.5-3-3-5。

-絕大部分記憶體可承受電壓為2.6~2.9v。

-設定不當"過低"DRAM參數將導致系統不開機。

-當您的記憶體非終生保固者,我們不建議您將DRAM電壓設定超過2.7v以上。

-當您的DDR為400以上,請酌量放大記憶體參數。

-當然,我們這邊講的是超頻...所以請選擇好一點的DRAM。 建議Hynix BT-D43、Hynix D5、SAMSUNG TCCD、BH-5、UCCC。

5.超頻HTT/FSB*與DRAM之關係

當您把HTT/FSB* 提升到超過200MHz的速度時,會造成一個問題,因為標準DDR400其

時脈為200MHz,提高HTT/FSB* 逾200MHz以上可能會導致系統無法開機。

您可以利用三個方法解決

1.使用FSB:DRAM比率(記憶體除頻)。

2.超頻DRAM。

3.購買廠商的超頻模組DRAM。

Ex:

當您有一顆大雕 3000+ 0448週期,

她可以一飛沖天,傲視群"U",HTT300Mhz,對她來說輕而易舉...

眼睛不眨一下就上了...

"可是您的DRAM卻只能跑DDR400~DDR500...... 怎麼辦??

選擇方案1(除頻)透過Bios設定:將DRAM時脈定頻/除頻。與HTT跑不相同的時脈。

選擇方案2(超頻)透過Bios設定:對記憶體加壓,放鬆參數。直接讓DRAM與HTT/FSB*跑同步。

選擇方案3(花錢):請洽詢您的荷包,以解決目前的困境。

6.超頻DRAM方式

-首先在Bios中讓您的DRAM與HTT/FSB*設定同步(AUTO),降低HTT,接著慢慢提昇您的HTT(提升HTT將會同時提升您的記憶體時脈)。此動作反覆測試直至無法開機。

-以在黑屏前的DRAM時脈下,測試memtest86

http://www.memtest86.com

-當然..失敗為成功之母..在您測試 memtest86 test 之步驟 5~6 卻總是過不了時...

請繼續下修HTT時脈 直到可以穩過測試 。此即是您的記憶體最佳時脈。

-有時候雖然能通過memtest86測試,但在OS中並無法通過Prime95測試。

-如果在您的MAX HTT下,記憶體無法以同步運行,您可以考慮加以除頻(上述方案1)。

7.除頻設定對照表 概略公式-"DRAM除頻時脈 = HTT時脈* 除頻比率"

除頻比率表(概略算法)

200 = HTT x 1 = 200

183 = HTT x .90 = Mhz

166 = HTT x .83 = Mhz

150 = HTT x .75 = Mhz

133 = HTT x .66 = Mhz

100 = HTT x .50 = Mhz

Ex:您的大雕3000+確定可以穩跑HTT280..

可是您的DDR卻是聯強DDR400..(只能穩跑200Mhz/DDR400)

套用公式,請找出您目前最佳的記憶體定頻/除頻方案??

解:

(此算法為概略值)

280*0.75(定頻150方案)=210Mhz=DDR420..噢噢~~要小心嚕。

280*0.66(定頻133方案)=184Mhz=DDR369 嗯...有點浪費...

8.記憶體除頻時脈值與公式所算出的值不相當?

-事實上記憶體時脈除頻值,並不是直接由HTT/FSB所得出的,它取決於CPU倍頻與記憶體除頻係數。這導致有時候DRAM時脈並不總是等於您所選定的比率計算結果。

-假設今天我們將HTT提高至250。而HTT:RAM=200:166=1:0.83

我們的DRAM時脈應該是250*0.83=207.5Mhz。然而實際上DRAM 卻是接近205Mhz。

這表示除頻後的值,並不總是非常精確的,而僅是近似。

-除頻真正的值應該是透過CPU的記憶體控制器來計算,但因為計算很複雜,故主機板廠商取一個概略的定義100/133/166/200 來代表。

9.真正的DRAM除頻計算方式

"(HTT)x記憶體除頻係數=DRAM除頻後時脈"

___________________________

-記憶體除頻係數 =【CPU倍頻 / [CPU倍頻 / 除頻比率] 】

-公式中 [CPU倍頻 / 除頻比率] 其值取整數,無條件進位,取至小數點後第一位。

-除頻比率=0.9、0.83.、0.75、0.66…..

1.當您設定的倍頻低過5時,記憶體控制器將以5除頻。

EX:

倍頻4,即使設定外頻與記憶體同步下

DRAM時脈實際為: 4/5=0.8,0.8* HTT200 = 160Mhz。

2.即使在CPU外頻與記憶體時脈同步下,當您的倍頻帶有小數點時,除頻比率為下一個整數倍頻值。

EX:

當您選擇9.5倍頻時

其記憶體除頻係數為 9.5/10=0.95,DRAM時脈=HTT*0.95

當您選擇10.5倍頻時

其記憶體除頻係數為 10.5/11=0.954,DRAM時脈=HTT*0.954

___________________________

Ex:假設HTT250、CPU倍頻9、DRAM設定除頻0.83 (200:166)

計算式如下

____________________________

記憶體除頻係數 =【CPU倍頻 / [CPU倍頻 / 除頻比率] 】

[CPU倍頻 / 除頻比率] = 9/0.83 = 10.84,因無條件進位,取至小數點第一位,得值11。

接著

HTT 250 x【 9 / [11] 】=250 x 0.8181 = 204.5454

DRAM時脈 = 204.5Mhz = DDR 409

____________________________

很複雜嗎??

為求簡便您可以概略使用HTT*除頻比率來計算您的DRAM時脈。

10.對DRAM除頻後會有什麼影響?

-因為超頻而選擇將HTT/FSB*與DRAM時脈不同步,此解決方式並不理想。

-以一個比率運行HTT/FSB* 與DRAM導致HTT/FSB* 與DRAM之間的傳輸效能延遲。若DRAM與HTT/FSB* 運行在相同時脈則無此問題。

-故欲獲得系統之最大超頻效能,使用超頻DRAM方案可能才是較為理想的。

-通常,若CPU因超頻後不穩,則除頻比率越大(0.9、0.83),系統穩定性越差。

________________________________________接續未完