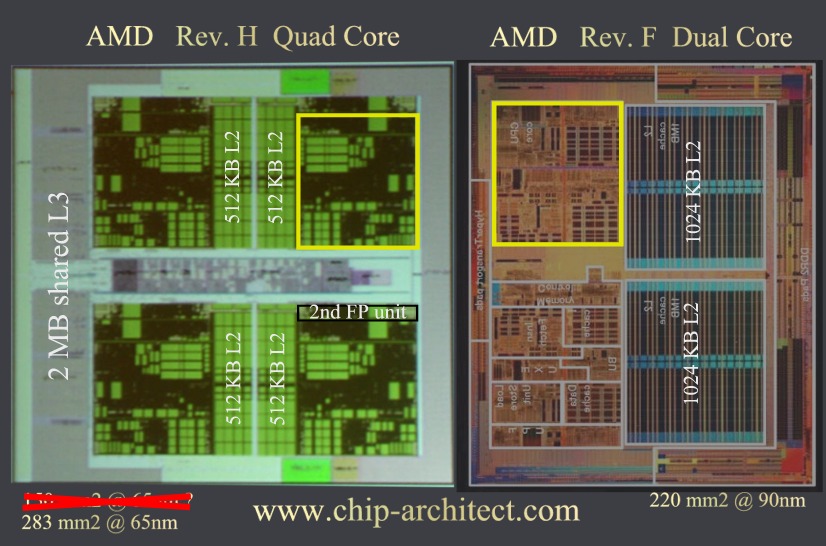

Realworld上David Kanter整理的比較詳細的detail:

0. Native quad core

1. Hypertransport up to 5.2GT/s

2. Better coherency

3. Private L2, shared L3 cache that scales up.

4. Separate power planes and pstates for north bridge and CPU

5. 128b FPUs - see 14,15

6. 48b virtual/physical addressing and 1GB pages

7. Support for DDR2, eventually DDR3

8. Support for FBD1 and 2 eventually

9. I/O virtualization and nested page tables

10. Memory mirroring, data poisoning, HT retry protocol support

11. 32B instead of 16B ifetch

12. Indirect branch predictors

13. OOO load execution - similar to memory disambiguation

14. 2x 128b SSE units

15. 2x 128b SSE LDs/cycle

16. Several new instructions

Coprocessors:

media processing

JVM/CLR acceleration

TOE, XML or SSL processing