|

PCDVD數位科技討論區

(https://www.pcdvd.com.tw/index.php)

- 系統組件

(https://www.pcdvd.com.tw/forumdisplay.php?f=19)

- - AMD Fusion第二波:CPU/GPU 2015年徹底融合

(https://www.pcdvd.com.tw/showthread.php?t=894507)

|

|---|

引用:

如果驗證是小事,那 AMD 為何連複雜度相對單純很多的 L3 都會出錯??? 當今隨便一顆主流晶片就能用掉數億顆電晶體,而且很快就會超過十億顆,驗證當真是小事??? 更不要說 HT 是二個執行緒共用一樣的解碼單元及執行單元...等,只要隨便一個環節的設計沒考慮清楚,不小心讓 B執行緒 的資料蓋掉 A執行緒 的資料,那就是天大的災難!你還認為驗證是小事!!! 題外話,K7~K10 也不是 AMD 原本的團隊所設計,套用你的邏輯這些產品都跟 AMD 沒關係,真是太扯了 :stupefy: 但有一點你說對了,Intel 家大業大...,總之其龐大的研發經費足以支撐各種架構或各種技術的開發,一時敗陣或一時犯錯都沒關係,只要下一代產品吸取經驗就能大幅贏回來,這才是 Intel 最可怕的地方 |

這是回#37的

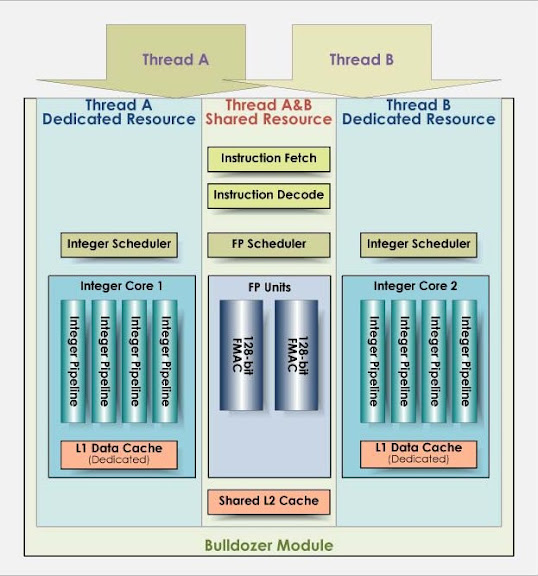

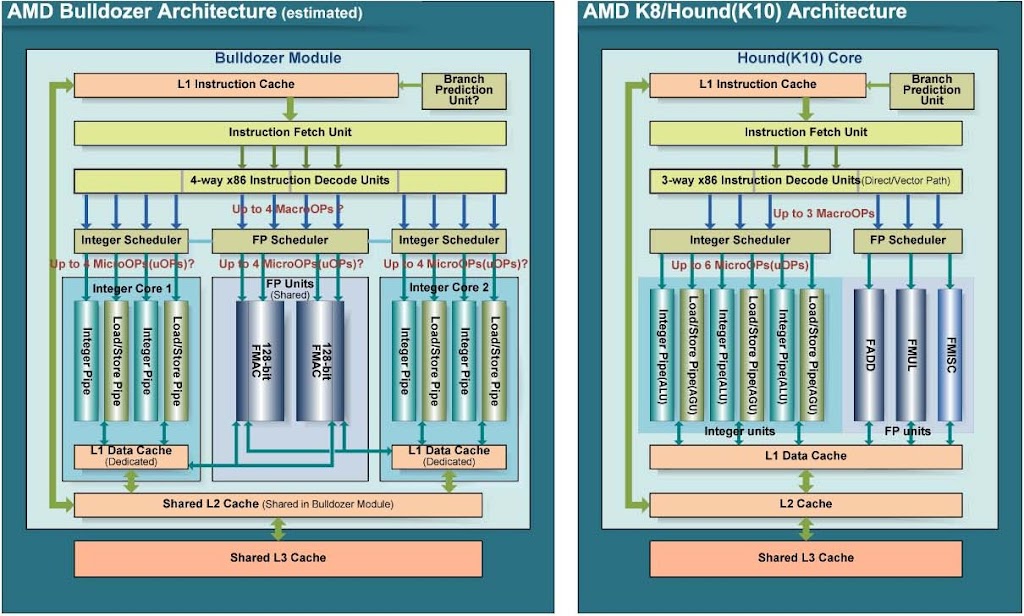

看圖片比較快  一個完整推土機最小完整單位是模組 如果稱一個最小完整單位為1 core,那推土機就是1M=1C2T 不過推土機比較接近於實體2core勝過於intel 的HT 所以一般人還是會直接說推土機是1M≒2C2T 這個推土機的1M跟K10的2C2T比起來效能低了一些 面積也小了一點 效能低的部位會出現在整數運算單元(K10有三個,推土機1M有四個->1核心兩個) AMD認為 CPU有三個整數單元有點矯枉過正 三個整數單元比起兩個來說 電晶體增加很多,效能只增加一些 現在AMD,intel的作法不同處在 AMD將核心單純化,可提昇使用效率、降低耗電(時脈可能因此受惠可以拉高一些) 單純化的結果是單執行緒會慢一些,把Performance/Watt 提高 多執行緒程式是它的優勢 intel則是核心複雜化,單執行緒、多執行緒都想要吃下來 耗電量增大 時脈可能拉不高 (在製程能力優於AMD的前提下,這些缺點可能不是問題) |

引用:

如果,稍微修改一下說法; 一個完整的區塊為 1 Block,那推土機就是 1B = 2C2T 兩顆整數處理核心 + 兩條執行緒 + 共用的浮點運算單元 問題在於推土機架構, 當資料一進來時就會分成兩條執行緒,進入兩個分開的整數核心內運算。 若有浮點運算需求,就會啟用核心共用的浮點運算功能。 這部分跟 Intel 的 HT 概念與實作又有所差異。 |

引用:

人之常情,一般是強者恆強 ...如果強者沒犯什麼錯誤的話 如果你是電機博士或博士後,AI兩家同時看上,一般人選I社的比例還是會比較多 更不用說如果是挖角,I社能給的利益也會比較大 |

你們講得都好深奧

那舉個例子------假設[推土機增加50%的面積 最高提升80%] 原始的CINEBENCH R10 1X分數為3800分 推土機架構1X為? 1. 3800 x 1.8 = 6840分 2. 3800 x 1.2 = 4560分 哪一個? |

引用:

這邊錯了,一個完整區塊就是一個模組(module) 不需要特別命名 一個模組有兩個整數核心,這兩個整數核心內各有兩個整數運算單元 1M≒2C2T,1C≒ 2 Integer Pipe + share L2 +share FPU 還是來個推土機跟K10的比對圖 比較快 草綠+藍綠為一個整數運算(Integer Pipe)  引用:

要看進來的執行緒是一個還是兩個,一個核心只會對應一個執行緒 引用:

要看產品才知道實際效應,如果要大略估計的話 那1模組的推土機架構依AMD的簡報提到效能為1.8倍的 K10 (單核心) 但應該要更保守一點估計為 1.6∼1.8倍 的K10 因為還要看該程式運算會不會很偏重整數部份 及 核心單純化後的時脈可以提高多少 |

所以推土機1Core到底是1cycle/4 MicroOP 還是2 MircoOP

2MircoOP的話那單核整數性能真的是倒退嚕了:jolin: 為什麼我看到很多地方都是寫4 MicroOP :confused: |

引用:

推土機架構圖中有關微指令的部分都是打問號,所以還是等真正的架構圖定案再說吧 但可確定的是每個整數核心中只有兩條整數管線,比前代少了一條 對不支援多執行緒的程式來說同時脈下的效能是一定會降低一些的 |

引用:

http://pc.watch.impress.co.jp/docs/...205_346902.html 因為K10是6個MicroOP(K7、K8也都是6個),推土機就算有4個 整數運算也已經是倒退了 這也是上一篇回覆我預估1.6倍的原因(1+2/3) 不過估錯了 整數運算最低應該估1.3倍才對 (2/3+2/3) 推土機單核心整數運算的架構類似於K6世代 未來筆電上的山貓、現在intel的atom 也都是這樣 不太一樣的是 Atom是in-order,AMD的是out-of-order (效能應該不會像Atom那樣離譜) |

主要是在看K7/K8/K10雖然是6 MicroOP(uOPs)

但是它上面的Instruction Decode Unit(指令解碼單元) K7/8/10-3Way (3-6-3) Bulldozer-4Way (4-4-2) 以Throughput峰值來說3way應該還是小於4way 所以我想整數應該還不至於會退化到K6-3 (2-4-2) |

| 所有的時間均為GMT +8。 現在的時間是04:09 PM. |

vBulletin Version 3.0.1

powered_by_vbulletin 2026。