|

PCDVD數位科技討論區

(https://www.pcdvd.com.tw/index.php)

- 系統組件

(https://www.pcdvd.com.tw/forumdisplay.php?f=19)

- - Intel 發表世界第一 22nm Trigate

(https://www.pcdvd.com.tw/showthread.php?t=928772)

|

|---|

半導體立體堆疊是不錯

不過良率的問題很大 散熱的要求增高 低功耗低發熱時還好說 一旦時脈拉高功耗一上升 那就是麻煩的開始 難不成將來的cpu散熱要做成夾心餅乾那樣 將兩頭都包起來 :laugh: 那接腳要怎麼連出來 :stupefy: |

引用:

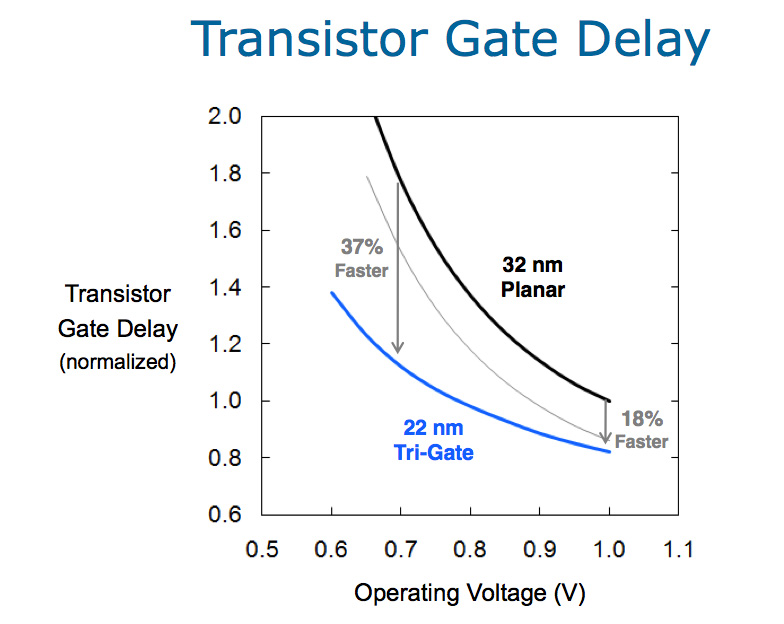

我不是相關專業出身 所以有誤還請糾正 這邊的電晶體效能與耗電都是跟 32nm Bulk 製程比較 (這次P1270 製程還有導入 High-K 跟 Tri-gate) 討論電晶體特性都會討論 Delay (Performance, 頻率) / Leakage (Power Consumption) 與電壓之間的關係 通常而言 電壓越大 Delay 越低, Leakage 越大, 製程間的特性曲線也不太一樣  引自pc.watch 在相較於32nm Bulk 製程, 22nm Tri-gate 可以在相同頻率下以75% - 80%的作業電壓下作業, Active Power 有50%的降低.  引自anandtech 在固定電壓狀況下, 在低電壓(0.7)有37%的效能增進, 在高電壓(1V) 也有18%增進.. 這些特性幾乎有跨兩個Process node的表現... |

引用:

這個技術 只是Transistor 的 Gate Oxide 跟 Inversion 接觸面由 Planar (2D) 變成立體包覆面 體積形狀幾乎沒有甚麼改變...散熱也不是問題... Die 本來就已經有好幾層了... |

引用:

是嗎? 請問聽誰說的? 如果好幾層DIE圖片早就好幾張了 |

|

多數人玩遊戲是不會手動超頻CPU的

|

引用:

毫秒嗎? |

引用:

應該是32nm 1v下的 delay 為 1單位的比例曲線 |

引用:

你說的這些在巴哈也有人發表 http://forum.gamer.com.tw/C.php?bsn...A=215695&tnum=9 意思大概是高階CPU也有10~15%的增進 受益最大的還是中低階以下的產品 很明顯是為了對抗ARM而來的 |

引用:

高階CPU 應該不會只有10~15%的增進, 整體 Power envelope (Active Power)降低後, 能塞的Core更多 或是 時脈可以拉更高... 為了對抗ARM? 這種技術已經談了有十年以上... 只是 Intel 實作較早量產.. TSMC 也會在16nm製程導入類似的 FINFET, 把製程技術 跟 ARM 對抗 搞在一起實在有點不妥... |

| 所有的時間均為GMT +8。 現在的時間是01:46 AM. |

vBulletin Version 3.0.1

powered_by_vbulletin 2026。