|

PCDVD數位科技討論區

(https://www.pcdvd.com.tw/index.php)

- 七嘴八舌異言堂

(https://www.pcdvd.com.tw/forumdisplay.php?f=12)

- - 採用3D垂直設計、突破縮放比例限制Samsung將量產V-NAND快閃記憶體

(https://www.pcdvd.com.tw/showthread.php?t=1020968)

|

|---|

吹氣球又不用本錢 :unbelief: :unbelief: :unbelief:

|

引用:

高性能、高容量看看這一家, Crossbar, Inc. 的RRAM會不會幹掉NAND Flash。 |

引用:

不會1234567890987654321 |

引用:

打個比方 NAND 1個bit = 1個火柴盒 要把NAND 容量做大的方法有: 1. 把面積做大,放更多火柴盒 2. 面積不變下把火柴盒做小, 也可以放更多火柴盒 3. 面積不變,火柴盒大小不變下, 把火柴盒切成2區(MLC)或3區(TLC) 4. 面積不變,火柴盒大小不變下, 把火柴盒做堆疊(疊24層容量就增加24倍) 這就是3D的概念 引用:

目前進度不明, 畢竟3D不是說做就做的出來的 尤其是NAND還滿GY的 1個bit掛掉, 那個Block就不能使用 疊越多層良率掉的速度肯定是雲霄飛車等級啊(說不定是火箭等級的) |

引用:

我沒說他不是3d立體結構,我只是說他不是"3d ic",而且這些根本老掉牙.. 他做這個都已經快10年了。要做很多層就算3d ic,你認為你現在用哪個mos 是只有一層的? 也絕對不存在你所謂3d做不做的出來問題,是一定做的出來,只是做成3d是不是能夠 更便宜並且解決遇到的困難,而你所謂那mlc,tlc更不是3d的概念,我印象中旺宏的網頁 寫得還蠻詳細的,你可以看看他們怎麼做be sonos的 |

引用:

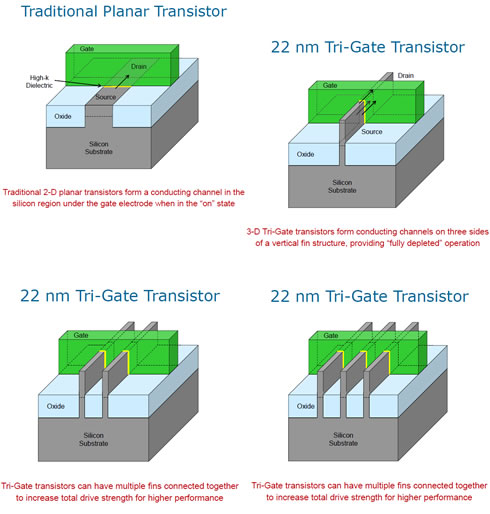

我想應該是我描述的不夠清楚 3D NAND個發展概念就是為了增加容量 當製程沒辦法再微縮, 搭上Multi Level Cell 或是 Triple Level Cell都無法再增加容量時 就會朝垂直方向的堆疊(就是第4點), 這才是3D NAND, 前面3點只是講古 至於MOS是不是只有一層 我想我應該用另一種說法 當你把現在2D MOS的gate dielectric 轉90度後跟3D MOS比 你就會發現, 現在的2D MOS確實只有一層 |

引用:

要放就放給你看  請問要怎麼轉planar transistor才不是3d? 2d mos只是相對於現在3d trigate而言,實際上他怎麼會不是3d?  intel跟ibm的copper wire interconnection又算不算你所謂的3d結構? 會搞成這樣的原因就跟前面的"無敵金鐘罩"犯了一樣的錯 他拿intel的"3d transistor"來說明3d ic,這兩者根本是完全不同的東西 你只要去搜尋一下甚麼是2.5D ic,甚麼是3d ic就知為啥我會說那不是3d ic 只是立體結構,而且已經做很久了.... |

我想你大概搞混了吧 如果你手上還有魔術方塊, 那你可以拿起來看看 假設有一個4x4x4的魔術方塊 每個魔術方塊的unit都是一個3維立方體 但是你把其中一層拿下來看 可以用(1,1)-->(4,4)標記出16個unit的位置 這叫2D NAND 當你拿出完整的4x4x4魔術方塊 你就必須用(1,1,1)-->(4,4,4)才能標記出這64個unit的位置 這叫3D NAND 我覺得我的解釋應該夠清楚了~_~+ |

你要扯就繼續扯下去吧...

反正爭贏沒獎品,反正我盡力說明3d mos,3d ct flash跟3d ic了 你要繼續把這東西當3d ic就隨你吧 |

引用:

3D IC 跟 3D NAND本來就不是同一件事 你可以用Vertical gate 3D NAND 或是 Vertical channel 3D NAND當關鍵字去找一下 基本上我講的就是現在3D NAND的定義, 這有什麼好扯的? 我只是如實的敘述一件事罷了 |

| 所有的時間均為GMT +8。 現在的時間是05:26 PM. |

vBulletin Version 3.0.1

powered_by_vbulletin 2025。